### А. И. Галушкин,

д.т.н., проф., зам. зав. кафедрой интеллектуальных информационных систем и технологий Московского физико-технического института, г. Долгопрудный, neurocomputer@yandex.ru

# Мемристоры в развитии высокопроизводительной вычислительной техники Аннотация

В данной статье излагается мнение автора о перспективах развития направления сверхпроизводительной вычислительной техники в связи с появлением мемристоров.

Ключевые слова: мемристоры, суперЭВМ, аналоговые вычисления, многослойные нейронные сети, клеточные нейронные сети.

#### Alexander I. Galushkin

Prof., Deputy Head of Chair of intelligent information systems and technologies of the Moscow Institute of Physics and Technology, Dolgoprudny, <a href="mailto:neurocomputer@yandex.ru">neurocomputer@yandex.ru</a>

## Memristor in high-performance computing development

**Abstract** This article presents the author's opinion about the prospects of this trend of super computing with the memristor invention.

#### Введение

Ниже представлена концепция разработки нейрокомпьютеров с применением мемристоров (Leon O. Chua. Memristor – The Missing Circuit Element. IEEE Transaction on circuit theory, CT-18, N 5, September, 1971), ориентированная на большое и очень большое число вычислительных элементов и, как следствие, на большое число мемристоров. Работа состоит из следующих разделов:

- 1. Предпосылки: архитектура вычислительных систем;

- 2. Предпосылки: теория нейронных сетей, нейроматематика, нейроуправление;

- 3. Предпосылки: реализация нейрокомпьютеров;

- 4. Выбор технологии изготовления мемристоров оценка производительности вычислительных систем с применением мемристоров;

- 5. Реализация нейрона с применением мемристоров;

- 6. Реализация нейронных сетей с применением мемристоров;

- 7. Настройка нейронных сетей с применением мемристоров;

- 8. СБИС нейрочипы с применением мемристоров;

- 9. Архитектура вычислительных систем с применением мемристоров;

- 10. Прикладные задачи;

- 11. Заключение.

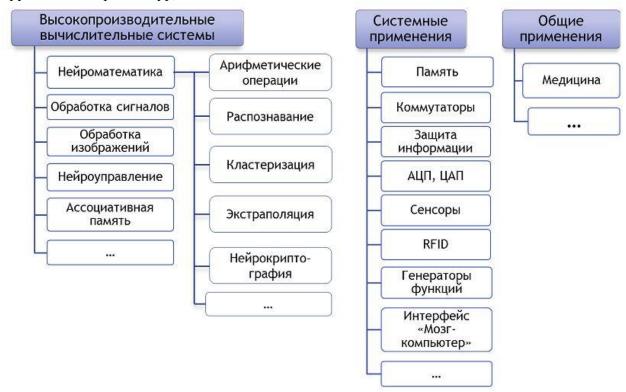

На рис. 1 условно представлена сфера применения мемристорных систем, сформировавшаяся. за последние несколько лет. Несомненно, эта сфера будет дополняться и расширяться. В данной работе в основном изложены основные принципы применения мемристоров при создании при создании и применении нейрокомпьютеров, как раздела сверхвысокопроизводительной вычислительной техники.

## 1. Предпосылки: архитектура вычислительных систем

В настоящее время высказываются серьезные сомнения в перспективности К-МОП технологии и других технологических решений для решения задачи перехода от петафлопного к экзафлопному уровню производительности вычислительных систем. В работе [1] представлено мнение двух известных экспертов: Харста Саймона и Томаса Стерлинга о том, что существуют серьезные сомнения в достижении к 2020 году производительности экзафлопного уровня  $(10^{18})$ . Основные сомнения касаются энергопотребления, которое для 10 петафлопной системы составляет 10 мегаватт, а для экзафлопной системы по расчетам должно достигать 2 гигаватт. В этой же работе

отмечается необходимость рассмотрения как других кроме КМОП-технологий, так и других типов архитектур, отличных от Фон-Неймановской.

Рис. 1. Функциональные задачи для мемристорных систем (уровень 2014 г.)

В настоящее время во всем мире реализуется несколько десятков подобных проектов. Одним из характерных проектов является представленный в работе [2].

В России разработана концепция создания вычислительных систем экзафлопного уровня с использованием классических принципов построения кластерных суперЭВМ, а также концепция развития высокопроизводительных вычислений на базе супернейрокомпьютеров [3].

Необходимо отметить два основных свойства современных суперЭВМ:

- Масштабируемость.

- Двухслойность архитектур.

С нашей точки зрения для перехода на экзафлопный уровень вычислений необходима реализация по крайней мере ещё одного шага: изменения логического базиса алгоритмов решения задач и, соответственно, элементной базы с переходом от носителя информации в виде уровней токов и напряжений в электрических схемах к носителю информации в виде частоты узких импульсов, подобно тому, как это имеет место в реальной нервной системе.

Основными предпосылками принципиального изменения архитектуры вычислительных систем при переходе к системам экзафлопной производительности являются следующие:

- Необходимость резкого повышения надежности за счет отказа от фон-Неймановской архитектуры вычислительных систем из элементов булевской логики И, ИЛИ, НЕ, когда в системе из значительного числа этих элементов происходит катастрофический отказ при отказе любого элемента;

- Необходимость резкого снижения энергопотребления за счет отказа от существующего позиционнного метода представления информации и перехода к другим, обеспечивающим снижение энергопотребления и как следствие, дополнительное повышение надежности;

• Необходимость резкого повышения однородности схемотехники элементов вычислительных систем, что должно привести к повышению эффективности при том резком увеличении интеграции элементов, которое будет иметь место при переходе к экзафлопной производительности.

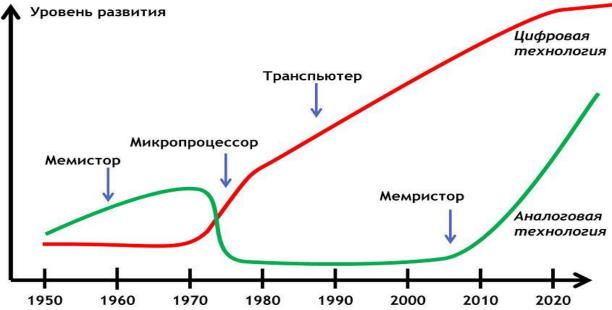

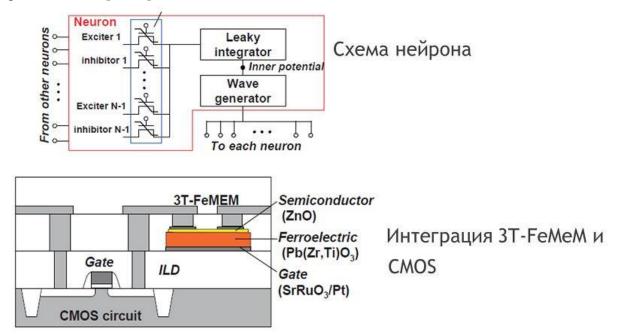

На рис. 2 отмечены основные этапы развития сверхвысокопроизводительной вычислительной техники за последние десятилетия. Отмечается, что мемристоры являются одним из эффективных путей развития данного вида техники на ближайшее десятилетие.

| Время | Производительность | Технология  Транспьютерные системы |  |  |

|-------|--------------------|------------------------------------|--|--|

| 1990  | 1 Гигафлоп/с       |                                    |  |  |

| 1999  | 1 Терафлоп/с       | Кластерные суперЭВМ                |  |  |

| 2009  | 1 Петафлоп/с       | Графические процессоры             |  |  |

| 2020  | 1 Экзафлоп/с       | Мемристоры                         |  |  |

Рис. 2. Этапы развития сверхвысокопроизводительной вычислительной техники за последние десятилетия.

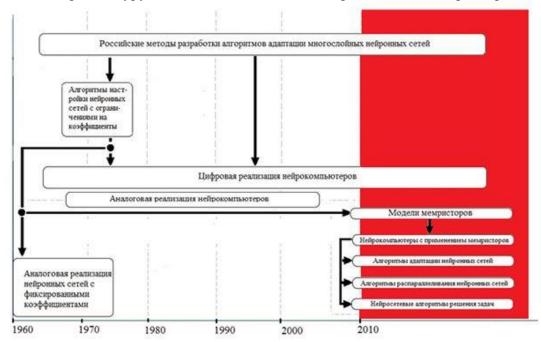

На рис. З условно представлена динамика развития технологий нейрокомпьютеров, начиная с 50ых годов прошлого столетия. В 50ые и 60ые годы прошлого столетия в основном для изготовления нейрокомпьютеров использовалась аналоговая технология при незначительной доле программной реализации на универсальных ЭВМ. С появлением микропроцессора, а также мощных универсальных цифровых ЭВМ, аналоговые ЭВМ в следствие их ограниченнной точности, несмотря на большое быстродействие, теряют свою роль, оставаясь в период 80ых, 90ых и даже 2000ых годов предметом разработки достаточно большого числа специализированных нейрочипов, наряду с большим числом разработок специализированных цифровых нейрочипов.

Рис. 3. Развитие технологий нейрокомпьютеров. Мемристоры – детище нанотехнологий.

Разработка мемристоров возрождает аналоговую обработку, резко понижая энергопотребление, увеличивая скорость обработки при контролируемой точности обработки, характерной для высокопараллельных нейросетевых структур с ограниченным числом слоев логической обработки.

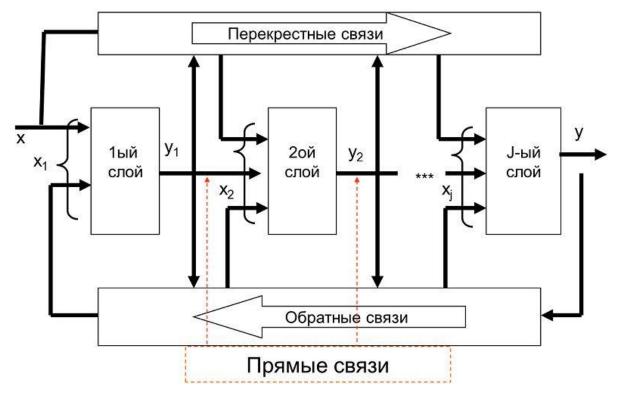

# 2. Предпосылки: теория нейронных сетей, нейроматематика и нейроуправление

Российская школа теории нейронных сетей зародилась в середине 60х годов прошлого столетия [4,5]. С самого начала этих работ применительно к адоптивным системам автоматического управления, нейронная сеть, как объект, управления, была выбрана в структуре, представленной на рис. 4. Нейронная сеть представляет собой высоко параллельную многослойную структуру с настраиваемыми последовательными, перекрестными и обратными связями.

Ниже представлена основная аксиоматика теории нейронных сетей, характерная для российской научной школы:

- Вероятностная модель мира;

- Нейронные сети логический базис решения любых задач;

- Разработка нейросетевых алгоритмов, специфичных для конкретной выбранной задачи;

- Отказ от использования субъективных нейросетевых парадигм;

- Нейронная сеть частный вид многомерного нелинейного динамического объекта управления;

- Любая идея нейросетевого алгоритма должна быть ориентирована на эффективную аппаратную реализацию в соответствие с текущей или перспективной технологией;

- Любая идея в части нейросетевых технологий не эффективна, если не может быть перенесена из одно- или двумерной иллюстрации на многомерную иллюстрацию.

Работы в области нейронных сетей получили развитие в [6,7,8].

В 2007 г. на международной конференции по нейронным сетям (IJCNN – 07, Orlando, USA) была организована российская секция «Overview of Soviet/Russian Neural Network R&D: The Untold Story» под руководством Роберта Хехт-Нильсена. Кроме ряда российских докладов была представлена монография [9] с предисловиями Лотфи Заде, Амари и Р. Хехт-Нильсона, которые отметили высокий уровень российских научных работ в этой области. Работа [10] является итоговой работой в этой области.

Нейроматематика — новый раздел вычислительной математики, связанный с разработкой нейросетевых алгоритмов решения сложных формализуемых и неформализуемых задач. Основные результаты российской научной школы в области нейроматематики представлены в работах [11,12,13].

Нейроуправление — это новый раздел теории управления, связанный с применением нейрокомпьютеров для идентификации и управления динамическими системами. Нейроуправление является направлением теории управления сложными системами:

- о сильно нелинейными;

- о с изменяемыми параметрами;

- о с изменяемой структурой;

- о многомерными;

- о распределенными.

Работы российской научной школы представлены в [14,15] и более десяти монографиях по прикладным задачам нейроуправления различными объектами.

Рис. 4. Многослойная нейронная сеть. Концепция 1967г.

#### 3. Предпосылки: реализации нейрокомпьютеров.

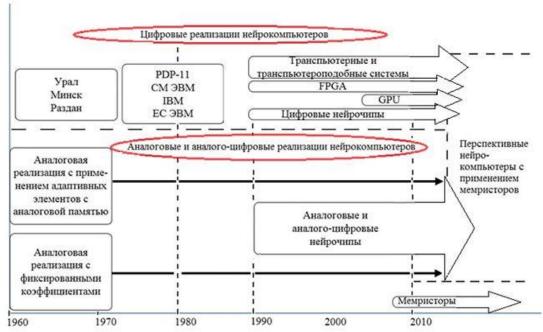

На рис. 5 представлены этапы развития реализаций нейрокомпьютеров в России:

- 60-ые годы прошлого века программные реализации на универсальных цифровых вычислительных машинах Урал, Минск, Раздан отечественного производства

- аналоговая реализация с применением мемисторов (Widrow et al. "Birth, Life and Death in Microelectronic Systems", Office of Naval Research Technical Report 1552-2/1851-1, May 30, 1961) аналоговых адаптивных элементов с аналоговой памятью [16,17].

Рис. 5. Развитие реализаций нейрокомпьютеров в России.

Ниже представлены основные направления исследований и разработок 60ых годов прошлого века в области адаптивных элементов с аналоговой памятью, которые потенциально были применимы для создания аналоговых нейрокомпьютеров

- 1. Магнитные элементы с аналоговой памятью.

- А. Метод суммирования приращений магнитного потока

- Б. Метод идеального намагничивания

- 1.1 Магнитные адаптивные элементы с аналоговой памятью на тороидальных ферритовых сердечниках.

- 1.2 Адаптивный элемент с аналоговой памятью на четных гармониках

- 1.3 Адаптивные элементы с аналоговой памятью на трансфлюксерах

- 1.4 Адаптивные элементы с аналоговой памятью на тонких магнитных пленках

- 1.5 Адаптивный элемент с аналоговой памятью на биаксе

- 1.6 Адаптивный элемент с аналоговой памятью, использующий явление магнитострикции.

- 2. Электрохимические адаптивные элементы с аналоговой памятью

- 2.1 Концентрационные электрохимические адаптивные элементы с аналоговой памятью.

- А. двухполюсные концентрационные электрохимические адаптивные элементы с аналоговой памятью, использующие визуальное и фотоэлектрическое считывание

- Б. Адаптивные элементы с аналоговой памятью, использующие концентрационные интегрирующие диоды

- В. Концентрационные интегрирующие тетроды

- 2.2. Электрохимические твердофазные адаптивные элементы с аналоговой памятью

- А. Мемистор

- Б. Ртутный адаптивный элемент с аналоговой памятью

- В. Электрохимический адаптивны элемент с аналоговой памятью, использующий фотоэлектрическое считывание

- 2.3. Адаптивные элементы, использующие выращивание токопроводящих путей.

- 3. Сверхпроводящие адаптивные элементы с аналоговой памятью

- 4. Конденсаторные адаптивные элементы с аналоговой памятью

- 4.1. Адаптивные элементы, использующие конденсаторы

- 4.2. Трансполяризатор.

- 5. Прочие адаптивные элементы с аналоговой памятью

- 5.1. Электромеханические адаптивные элементы

- 5.2. Адаптивные элементы с аналоговой памятью на термисторе

- 5.3. Металлоокисные адаптивные запоминающие элементы

Реализация аналоговых нейрокомпьютеров с использованием адаптивных элементов с аналоговой памятью в 60е годы прошлого века оказалась слишком громоздкой и дорогостоящей. Кроме этого существенным недостатком подобных реализаций нейрокомпьютеров являлось достаточно большое время перестройки коэффициентов нейронных сетей.

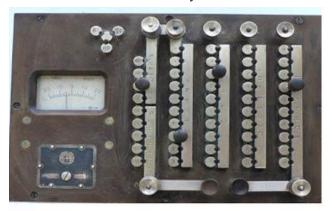

На рубеже 60-ых и 70-ых годов прошлого столетия для применения аналоговых нейрокомпьютеров был выбран класс задач для которых сбор архива машинных данных для обучения был достаточно длительным и дорогостоящим. При этом необходимость в перестройке коэффициентов нейронных сетей либо отсутствовала, либо была необходима через значительный период времени (1 месяц, 1 год и т.д.). Для этих целей были реализованы аналоговые нейрокомпьютеры с коэффициентами проставляемыми вручную (рис. 6,7,8).

Период 70-ых, 80-ых годов прошлого столетия был периодом программной реализации нейрокомпьютеров на микропроцессорах и универсальных ЭВМ различного типа (PDP-11, IBM, их общегражданских и специальных отказоустойчивых аналогов).

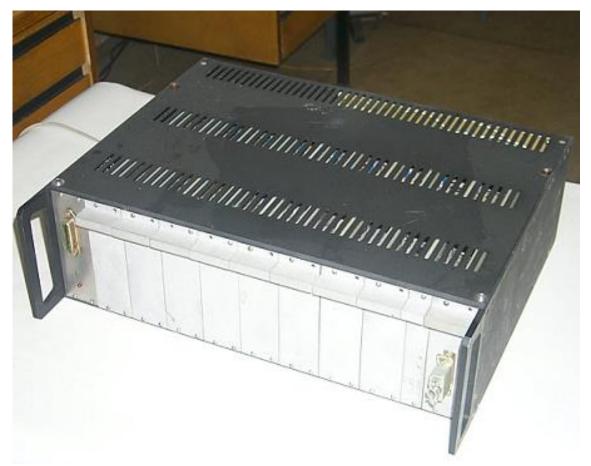

Рис. 6. Нейрокомпьютер (1970).

Рис. 7. Функциональная структура нейрокомпьютера 1970 года.

Рис. 8. Общий вид нейрокомпьютера 1974 г. Размерность входных признаков 30 Число классов 8

Начало 90-ых годов прошлого века характеризовалось сразу несколькими направлениями разработок нейрокомпьютеров, связанных с развитием технологии микроэлектроники:

- программные реализации нейрокомпьютеров на базе транспьютерных систем (десятки, сотни процессоров с сопроцессорами обработки сигналов и изображений);

- нейрокомпьютеры на базе ПЛИС (программируемых логических интегральных схем);

- цифровые, цифро аналоговые и аналоговые нейрочипы.

Эти разработки в значительной степени отражены в монографии [18]. Однако в этот период времени еще не пропал интерес к аналоговой или аналого-цифровой реализации нейрокомпьютеров, подобных представленным на рис. 6,7,8 с модификацией для решения задач распознавания сигналов по форме. Подобный нейрокомпьютер был построен еще в начале 70-х гг. прошлого века для решения задач распознавания типа сердечных заболеваний по реоэнцефалограмме (РЭГ) — измеряемой внешним датчиком проводимости сердечной мышцы.

В 1992 г. в передаточной функции нейрона была использована модель бесконечного числа признаков периодического сигнала. При этом передаточная функция нейрона 1-го слоя имела следующий вид:

$$y = sign \int_{0}^{T} a(i) * x(i)di$$

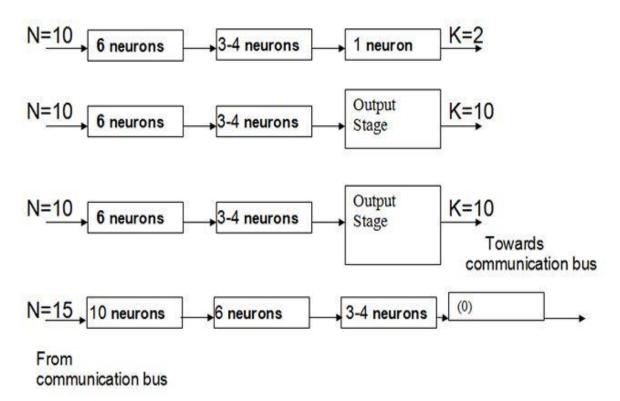

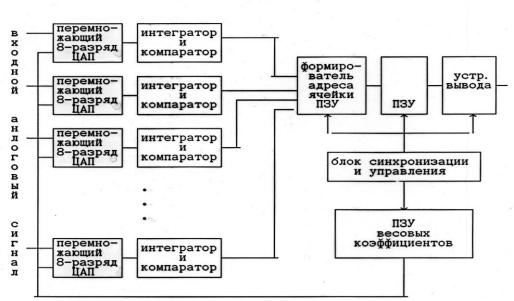

Для реализации подобных континуальных нейронов использовались БИС многоканальных АЦП-умножителей аналоговых сигналов. На рис. 8а представлена блоксхема аналого-цифрового нейрокомпьютера распознавания периодических сигналов по форме, а на рис. 8б фото образца данного нейрокомпьютера.

#### БЛОК-СХЕМА АНАЛОГОВОГО НЕЙРОКОМПЬЮТЕРА

Рис. 8а. Блок-схема аналогового нейрокомпьютера

Рис. 8б. Общий вид аналого-цифрового нейрокомпьютера для распознавания сигналов по форме. (1992 г)

Ниже представлены основные технические характеристики аналого-цифрового нейрокомпьютера:

# **Технические характеристики аналого-цифрового нейрокомпьютера:**

Нейрокомпьютер (АНЦК) предназначен для входного контроля микросхем памяти серий RUx (x = 2, 4, 8, 12). В АНЦК реализована континуальная трехслойная нейронная сеть, синтезированная по парадигме нейронных сетей с переменной структурой.

1. Диапазон входного сигнала 0-3 B. 2. Приведенная погрешность обработки входного сигнала 5%. 3.Полоса сигнала 200 Кгц 5 Мкс. 4.Тактовая частота 5. Входы аналогового нейрокомпьютера: - аналоговый - тактовый. 6.Запуск -внешний по сигналу цикла, - внутренний от тест-генератора. 7. Количество классов 8. Количество нейронов - не более 8 (І вариант) - не более 16 (II вариант) 9.Размерность весовых коэффициентов 8 бит. 10. Весовые коэффициенты хранятся в ППЗУ и могут быть изменены заменой ППЗУ 11. Результаты классификации индицируются на передней панели с помощью светодиодов 12. Конструкция АНК выполнена в виде настольного блока в стандарте "Евромеханика" размером 3U. 13.Питание от сети переменного тока 220 в 50 гц

Период 2005 — 2007 г.г. характеризуется активным становлением суперЭВМ на базе графических процессоров и началом разработки для них программных эмуляторов больших нейронных сетей [19].

В настоящее время (рис. 5) научно-технический задел для разработки будущих нейрокомпьютеров с применением мемристоров составляют:

- программные реализации нейронных сетей на транспьютерных и кластерных суперЭВМ;

- реализация нейрокомпьютеров на ПЛИС;

- программные реализации нейрокомпьютеров на суперЭВМ на базе графических процессоров;

- многолетние разработки цифровых, аналого-цифровых и аналоговых нейрочипов являются научно-техническим заделом будущих разработок нейрокомпьютеров с применением мемристоров.

# 4. Выбор технологии изготовления мемристоров. Оценка производительности вычислительных систем с применением мемристоров.

Мемристоры изготавливаются на базе нескольких технологий

- 1. Электрохимические элементы

- 2. Оксид титана

- 3. Оксид танатала

- 4. Полимеры

- 5. Ферроэлоектрики

- 6. Углеродные нанотрубки

- 7. Кремний

- 8. Аморфный кремний

- 9. Поликремний

В результате разработок реализуются мемристоры, мемристорные матрицы и мемристорные системы с различными физическими свойствами, которые необходимо оценивать с точки зрения их применимости в конкретных структурах вычислительных систем.

Применимость той или другой технологии изготовления мемристорных систем необходимо оценивать как с точки зрения существующих критериев оценки производительности, так и с точки зрения оценки производительности будущих нейрокомпьютеров с применением мемристоров.

Производительность нейрокомпьютеров с применением мемристоров должна оцениваться с точки зрения следующих количественных показателей:

- Число эмулируемых нейронов;

- Число эмулируемых связей;

- Число переключений связей в секунду;

- Потребляемая мощность;

- Число физических переключений до момента отказа (дополнительно);

Расчет производительности мемристорных систем при анализе технологий должен производиться на нескольких уровнях:

- на уровне элементарных операций;

- на уровне базовых нейросетевых систем на мемристорах;

- на уровне СБИС с учетом внутренней коммуникационной среды;

- на уровне плат с учетом внутриплатной коммуникационной среды;

- на уровне блоков с учетом внеплатной коммуникационной среды;

- на уровне супернейрокомпьютера с учетом межблочной коммутационной среды.

Необходимо высказать некоторое предостережение тем, кто будет оценивать производительность мемристорных систем. В истории развития вычислительной техники известны примеры, когда оптимистическая оценка производительности на уровне элементарных операций предлагаемой технологии оказывалась несостоятельной при распространении оценки производительности на более общие архитектурные элементы , платы, блоки, стойки, и т.д. и при расширениикруга реализуемых алгоритмов (т. е. в попытке сделать вычислительную систему более универсальной). Так произошло с оптическими ЭВМ, в которых элементарные операции (перемножение матриц) выполнялись очень быстро, однако системы так и не стали универсальными. То же произошло с транспьютерными системами с сопроцессорами обработки сигналов и изображений IMSA100, IMSA110 фирмы Inmos, в которых операции умножения-сложения выполнялись очень быстро, но в конкретных структурах одномерных и двумерных аппаратно реализованных Z-фильтров.

Начало исследования производительности мемристорных систем необходимо проводить разработкой инструментальных система исследования мемристоров и мемристорных матриц, включая следующие этапы:

- 1. Исследование, разработка и экспериментальная реализация принципов стыковки мемристорных матриц с элементами КМОП-технологии.

- 2. Разработка инструментальной системы для исследования мемристорных матриц с выходом на персональную ЭВМ, включая драйвер.

- 3. Разработка контроллера на ПЛИС для стыковки мемристорных систем с персональными ЭВМ, с драйвером.

- 4. Экспериментальная и теоретическая оценка понижения энергопотребления в мемристорных системах при переходе к представлению сигналов в виде частотно модулированной последовательности импульсов.

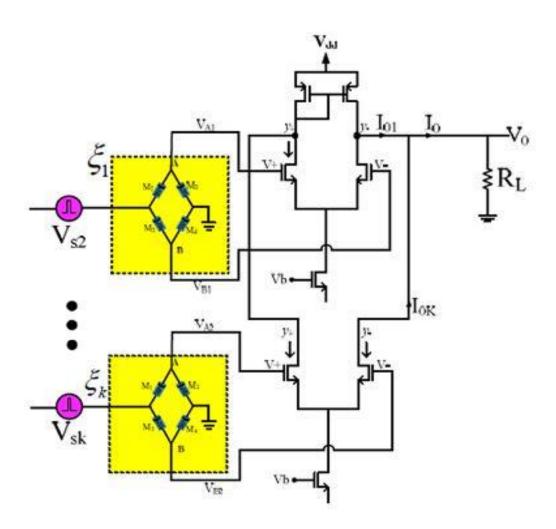

### 5. Реализация нейрона с применением мемристоров.

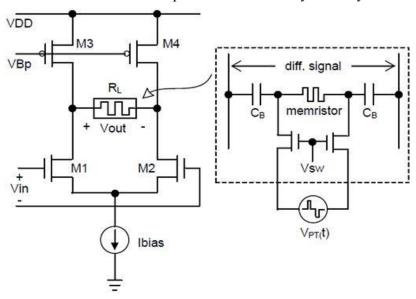

В схемной реализации нейрона мемристоры выполняют функцию синапсов – перестраиваемых весовых коэффициентов. Возможно несколько вариантов применения мемристоров для этой цели. Ниже представлены несколько известных вариантов, требующих доработки с точки зрения включения нейрона в схему нейронной сети и с точки зрения включения схемы нейронной сети в общую схему СБИС-нейрочипа.

Рис. 9. Реализация синапаса нейрона с применением мемристора.

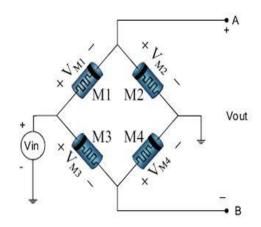

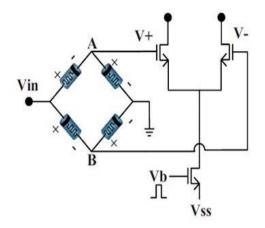

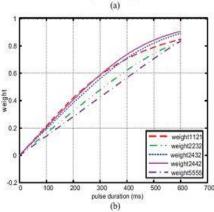

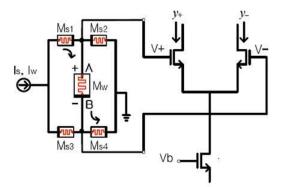

В работе [20] представлен один из вариантов реализации синапса нейрона с применением мемристоров (рис. 9). Вариант принципиальной схемы многовходового нейрона представлен на рис. 10 [21]. На рис. 11 представлена мостовая схема соединения мемристоров, обеспечивающая реализацию положительных и отрицательных значений весовых коэффициентов в нейронной сети [22]. В той же работе в развитие мостовой схемы соединения мемристоров представлена схема синапса с мостом из мемристоров (рис. 12) и расчетные результаты поведения мемристоров (рис. 13):

Рис. 10. Схема трехвходового нейрона с применением мемристоров.

Рис. 11. Схема мемристорного моста.

Рис. 12. Схема синапса с мостом из мемристоров

а) Программирование положительных и отрицательных весовых коэффициентов с идентичными мемристорами в мосту

б) Программирование положительных весовых коэффициентов для идентичных мемристоров

Рис. 13. Расчетные результаты поведения мемристоров

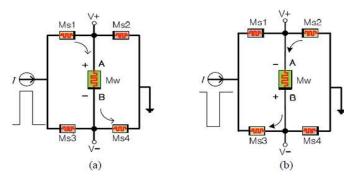

В работе [23] представлен другой вариант соединения мемристоров в схеме синапса (рис. 14) и предлагается схема изменения знака весового коэффициента в синапсе, представленная на рис. 15.

В соответствии с мостовыми схемами соединения мемристоров, представленными в [22] в работе [24] представлена схема нейрона с несколькими мемристорными входами (рис. 16).

Рис. 14. Вариант реализации синапса с применением мемристоров.

Рис. 15. Предлагаемая схема изменения знака весового коэффициента в синапсе с применением мемристоров.

- а) Положительная конфигурация

- б) Отрицательная конфигурация.

Рис. 16. Схема нейрона с несколькими мемристорными входами.

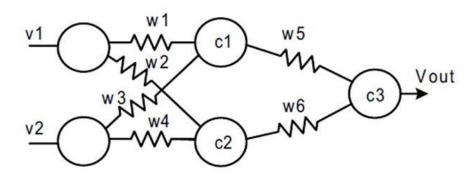

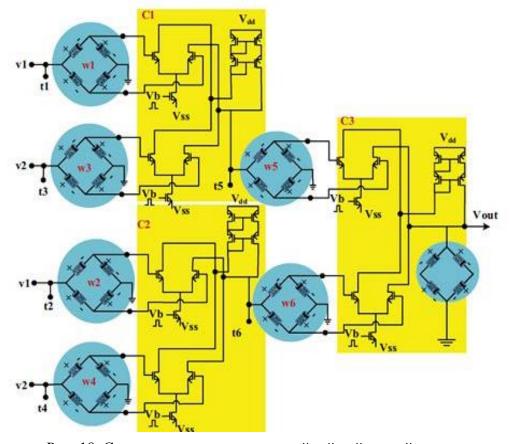

## 6. Реализация нейронных сетей с применением мемристоров.

На рис. 17 представлена простейшая двухслойная нейронная сеть, ориентированная на реализацию с применением мемристоров [22], а на рис. 18 её реализация с применением мемристоров.

Рис. 17. Типовая двухслойная нейронная сеть.

Рис. 18. Схемная реализация двухслойной нейронной сети.

Анализ публикаций 2008 – 2014 годов показал, что попытки реализации нейронных сетей с применением мемристоров касаются в основном многослойных нейронных сетей следующих видов:

- с полными последовательными связями;

- с обратными связями (рекуррентные нейронные сети);

- клеточные нейронные сети, ориентированные на обработку изображений.

Рассматриваются нейронные сети, ориентированные на достаточно узкий класс прикладных задач:

- бинарные нейронные сети с бинарным многомерными входными сигналами и бинарными (0, 1) коэффициентами;

- RBF нейронные сети;

- СМАС нейронные сети.

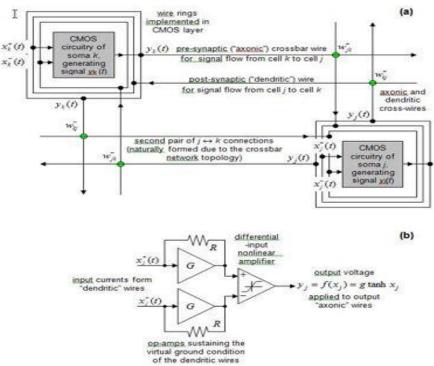

В работе [25] предложена (рис. 19) схема реализации весового коэффициента с мемристорами для клеточной нейронной сети. В работе [26] предложена другая схема применения мемристоров в клеточной нейронной сети (рис. 20).

Рис. 19. Схема реализации весового коэффициента с мемристорами для клеточной нейронной сети

Рис. 20. Связь между одной парой клеток в сети CrossNet.

Разработка и реализация принципиальных схем нейронных сетей различных структур с применением мемристоров является предметом дальнейших исследований в ближайшие годы.

## 7. Настройка нейронных сетей с применением мемристоров;

С нашей точки зрения, работы по реализации алгоритмов настройки нейронных сетей с применением мемристоров имеют самый начальный характер и в основном касаются реализации простейших алгоритмов типа правила Хебба [27]. Ориентация мемристоров, как детища наноэлектроники, на реализацию нейронных сетей с большим и очень большим количеством нейронов и настраиваемых коэффициентов, сделает задачу разработки и реализации алгоритмов настройки важной, сложной, в значительной степени определяемой архитектурой будущих вычислительных систем мемристоров.

Замечание: Отметим, что правило Хебба, в его логическом варианте, в России было реализовано диалоговым интерактивным режимом работы в мостовой системе прецизионного измерения сопротивления (рис. 21,22), выпускаемой во время 2ой Мировой войны сотнями тысяч штук.

Рис. 21. Отечественный прецизионный измеритель сопротивления, функционирующий по правилу – аналогу правила Хебба.

Рис. 22. Фирменная бирка с серийным номером прецизионного измерителя сопротивления.

В работе [28] представлен аналитический подход к сравнению простейших алгоритмов настройки применительно к мемристорным системам. Эти методы требуют развития как с точки алгоритмов адаптации, используемых в Mathlab (Neural Network Toolbox), так и с точки зрения алгоритмов адаптации нейронных сетей, учитывающих ограничения на весовые коэффициенты [5,6,8,9,10]. Условно, если в 60-ые годы прошлого века алгоритмы настройки формировались для нейронных сетей как объекта управления:

$$y = f \sum a_3 \cdot f \sum a_2 \cdot f \sum a_1 \cdot x$$

$y=f\sum a_3\cdot f\sum a_2\cdot f\sum a_1\cdot x$  с ограничениями на коэффициенты 1,2,3-его слоев нейронной сети, то для мемристорных систем эти алгоритмы должны формироваться для более сложного объекта:

$$y = f \sum_{z} a_3(z) \cdot f \sum_{z} a_2(z) \cdot f \sum_{z} a_1(z) \cdot x$$

Здесь: х – входной сигнал нейронной сети;

у – выходной сигнал нейронной сети;

f – функция активации нейрона.

$a_1(z), a_2(z), a_3(z)$  — передаточные функции мемристоров, формируемые моделями в системах PSpice, Cadence, Mathlab.

На рис. 23 представлена общая структура работы по созданию алгоритмов настройки нейронных сетей с применением мемристоров. Для нейрокомпьютеров с применением мемристоров с использованием моделей мемристоров на базе созданных алгоритмов настройки многослойных нейронных сетей с учетом ограничений на коэффициенты необходимо разработать специфические для мемристорных систем:

- алгоритмы адаптации нейронных сетей;

- алгоритмы распараллеливания нейросетевых алгоритмов с контуром адаптации на архитектуру вычислительных систем с применением мемристоров.

Рис. 23. Общая структура работ по созданию алгоритмов настройки сетей с применением мемристоров.

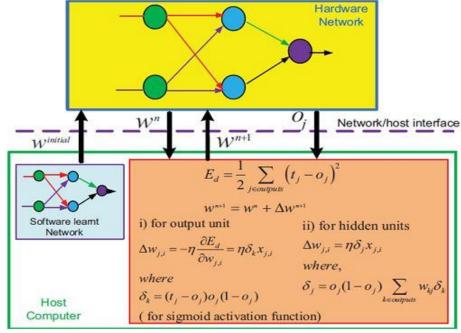

В связи с этим представленная в [22] схема обучения нейронной сети с применением мемристоров с реализацией блока настройки на хост-ЭВМ вряд ли жизнеспособна для вариантов с большим числом мемристоров (рис. 24).

Распараллеливание алгоритмов адаптации и требование повышения быстродействия должны привести к внутрикристальной реализации алгоритма обучения, причем на цифровом и аналоговом уровне.

Рис. 24. Схема обучения многослойной нейронной сети.

#### 8. СБИС – нейрочипы с применением мемристоров.

Разработка СБИС-нейрочипов с применением мемристоров является одним из важнейших направлений работ в области создания перспективных нейрокомпьютеров. При этом необходима аналитическая работа для обеспечения качественной разработки мемристорных систем, в том числе:

- Анализ разработок адаптируемых систем с аналоговой памятью 60-ых 70-ых годов прошлого столетия с целью использования в современных разработках мемристорных систем.

- Анализ разработок аналоговых и аналогово-цифровых нейрочипов последних десятилетий с целью использования в современных разработках мемристорных систем.

При этом анализ разработок аналоговых и аналого-цифровых нейрочипов должен касаться следующих разделов:

- аналоговые нейрочипы;

- аналого-цифровые нейрочипы;

- клеточные нейрочипы;

- нейрочипы с частотно-импульсным представлением сигналов;

- оптические и оптоэлектронные нейрочипы;

- молекулярные нейрочипы

- специализированные аналоговые и аналого-цифровые нейрочипы:

- АЦП;

- CMAC;

- обработки изображений;

- нейроуправления;

- ассоциативной памяти;

- обработки речевой информации;

- другие

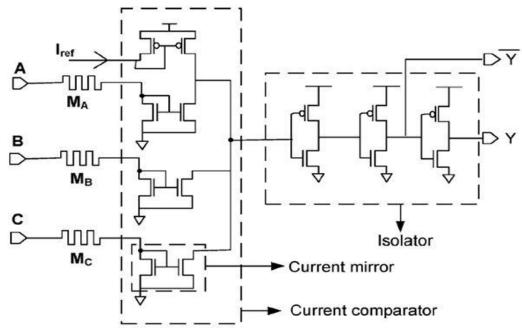

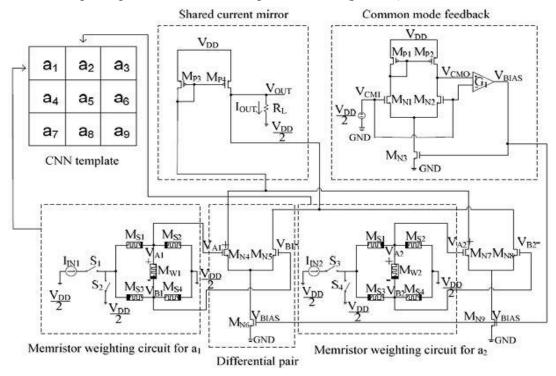

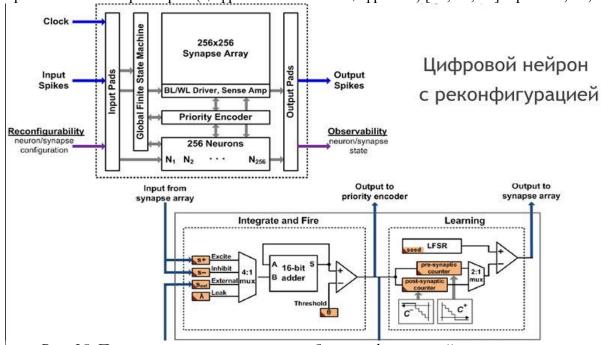

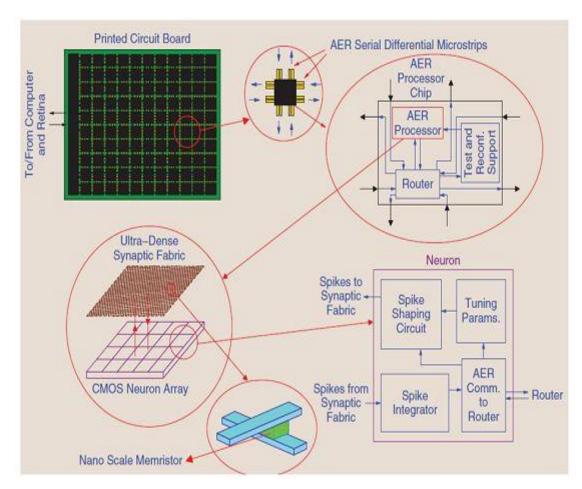

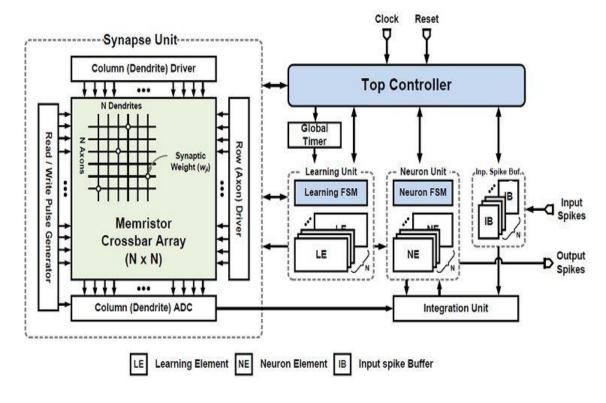

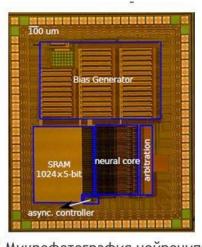

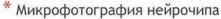

Типичным примером домемристорной разработки цифровых нейрочипов с частотно-импульсной модуляцией сигналов является схема, представленная на рис. 25 [29]. Необходимо отметить несколько попыток реализации СБИС-нейрочипов с применением мемристоров (цифровых и аналого-цифровых) [30, 31, 32] – рис. 26, 27, 28.

Рис. 25. Пример домемристорных разработок цифровых нейрочипов с частотно-импульсной модуляцией сигналов.

Рис. 26. Вариант архитектуры цифрового нейрочипа с применением мемристоров.

Рис. 27. Вариант архитектуры цифрового нейрочипа с применением мемристоров.

Схема синапсов

Рис. 28. Аналого-цифровой нейрочип с применением мемристоров.

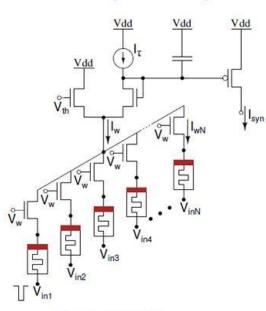

Особое внимание нужно обратить на разработку нейрочипа с применением трехтерминального ферроэлектрического мемристора [33] — рис. 29 (в отличие от наиболее широко распространенных в настоящее время двутерминальных мемристоров), в значительной степени идеологически повторяющего разработки мемисторов 60ых годов прошлого века [16,17].

Рис. 29. Нейрочип с применением трехтерминального ферроэлектрического мемристора.

## 9. Архитектура вычислительных систем с применением мемристоров.

На рис. 30 представлена общая архитектура перспективного супернейрокомпьютера с применением мемристоров. Классические варианты хост-ЭВМ и кластерного ядра дополняются в данной архитектуре двумя типами блоков:

– системы на базе ПЛИС (БМК) с частотно-импульсным представлением сигналов и мемристорных систем коммутации, как программно-аппаратный эмулятор нейронных сетей;

аналого-цифровая часть, реализованная на СБИС – нейрочипах с применением мемристоров.

Рис. 30. Архитектура перспективного супернейрокомпьютера с использованием мемристоров

Результатами работ по разработке технических средств супернейрокомпьютера с применением мемристоров должны быть:

- Архитектура и экспериментальные образцы каскадируемых СБИС на базе мемристорных матриц для использования в перспективных супернейрокомпьютерах.

- Архитектура и экспериментальные образцы базовых каскадируемых плат в конструктивах PCI, microPCI, VME с использованием СБИС на базе мемристоров для использования в перспективных супернейрокомпьютерах.

- Архитектура и экспериментальные образцы базовых каскадируемых блоков с использованием плат в конструктивах PCI, microPCI, VMЕдля использования в перспективных супернейрокомпьютерах.

- Оформление патентов на архитектуры СБИС, плат и блоков на базе мемристорных матриц.

Структура системного программного обеспечения перспективного супернейрокомпьютера с применением мемристоров должна состоять из следующих разделов:

- Общее системное программное обеспечение (ОС, компиляторы и пр.);

- Алгоритмы и программы распараллеливания нейронных сетей различной структуры;

- Вариант MPI;

- Вариант системы типа Foundation для ПЛИС с применением мемристоров;

- Алгоритмы и программы настройки нейронных сетей с учетом ограничений мемристоров.

Для разработанных вариантов архитектур должна быть проведена общая оценка качества вычислительных систем с использованием мемристоров, в том числе:

- Разработка и апробация методики количественной оценки производительности суперкомпьютеров на базе мемристоров;

- Разработка методики обеспечения и оценки необходимой точности вычислений при переходе в супернейрокомпьютере к аналоговой обработке;

• Оценка понижения энергопотребления в супернейрокомпьютере при переходе к представлению сигналов в виде частотно-модулированной последовательности узких импульсов.

## 10. Прикладные задачи.

Текущее состояние интереса авторов к решению прикладных задач на вычислительных системах с применением мемристоров условно можно представить схемой, изображенной на рис. 1.

Необходимо отметить соответствие структуры и параметров реализуемых нейронных сетей с применением мемристоров классу решаемых задач

- Структуры нейронных сетей:

- многослойные нейронные сети;

- 2D и 3D клеточные нейронные сети;

- реккуррентные нейронные сети;

- хаотические нейронные сети;

- Разрядность коэффициентов нейронных сетей:

- 1:

- K:

- управляемая разрядность;

- плавающая запятая;

- Скорость изменения коэффициентов

- нулевая;

- средняя;

- большая.

Большие нейронные сети — главная задача реализации нейрокомпьютеров с применением мемристоров. Как следствие — выбор для решения на мемристорных системах сложных задач:

- Обнаружение атак на информационные ресурсыв больших распределенных вычислительных сетях;

- Нейрокриптография;

- Уравнения математической физики, включая генерацию адаптивных сеток;

- Обработка видеоизображений и медиаинформации (проблема big data);

- Создание 3D моделей мозга;

- Управление плазмой;

- Обработка геномной и протеомной информации;

- Любые другие применения нейрокомпьютеров, где необходимо увеличить отношение производительности к стоимости или энергопотреблению.

Ниже сделана попытка ранжировать по некоторым признакам наиболее важные, с нашей точки зрения, сложные задачи с применением эффективных программно-аппаратных нейросетевых эмуляторов. Ниже в таблице и на рис.31 представлен, конечно, неполный перечень сложных задач для решения с применением сверхвысокопроизводительной вычислительной техники.

|                            | Объект       | Подгото       | Подгот       | Социал     | Форма   | Отсутс       |

|----------------------------|--------------|---------------|--------------|------------|---------|--------------|

| Признаки                   | ивная        | влен-ность в  | овленность в | ьная       | лизация | твие         |

|                            | готовность   | части решения | части        | значимость | задачи  | формализации |

|                            | перехода в   | на GPU        | решения на   | задачи     |         | задачи       |

| Задачи                     | нейросетевой |               | FPGA         |            |         |              |

|                            | логический   |               |              |            |         |              |

|                            | базис        |               |              |            |         |              |

| Обнаружение атак           |              |               |              |            | -       | +            |

| Нейрокриптография          |              |               |              |            | +       | +            |

| Уравнения мат.физики       |              |               |              |            | +       | -            |

| Big data                   |              | ı             |              |            | -       | -            |

| Нейроуправление<br>плазмой |              |               |              |            | -       | +            |

| Геномика и протеомика      |              |               |              |            | -       | +            |

| Биометрические<br>системы  |              |               |              |            | -       | +            |

| Модели разделов мозга      |              |               |              |            | -       | +            |

Рис 31. Признаки задач, предполагаемых для решения на будущих супернейрокомпьютерах с применением мемристоров

Здесь нам важно показать основные принципы подхода (желательно неэмоционального) к выбору задач для решения на будущих супернейрокомпьютерах с применением мемристоров. При этом необходимо сделать несколько замечаний к данной таблице, которые, конечно, являются субъективным мнением автора.

## 1. Обнаружение атак.

Анализ литературы за последние 10-12 лет показал, что нейросетевые алгоритмы в последние годы занимают в решении этой задачи основное место. Это касается в первую очередь нейросетевых алгоритмов кластеризации и классификации, обучаемых на тестовых и реальных последовательностях сообщений.

Заказчики понимают, что для важных государственных систем с большими потоками информации задача обнаружения атак на информационные ресурсы требует больших вычислительных ресурсов и в первую очередь может быть реализована с помощью суперЭВМ на базе графических процессоров, либо с помощью нейрокомпьютера, реализованного на FPGA.

Социальная значимость данной задачи высоко оценивается как в России, так и за рубежом.

Данная задача является частично формализуемой, в основном в части алгоритмов подготовки пространства признаков, но в основной своей части (кластеризация и классификация) является неформализуемой.

#### 2. Нейрокриптография.

Объективная необходимость перехода в нейросетевой логический базис в значительной степени определена зарубежными работами [35] и в некоторой степени сформирована в России.

Социальная значимость криптографической защиты информации высока и в России, и за рубежом. Во множестве криптографических задач присутствуют как формализуемые, так и неформализуемые постановки [35].

#### 3. Уравнения математической физики.

Несмотря на достаточно большое количество научных работ, в том числе и монографий по нейросетевым алгоритмам решения задач математической физики, все же нейросетевые алгоритмы пока не получили широкого распространения. Основной причиной этого является широкое распространение для решения этих задач кластерных суперЭВМ и суперЭВМ на базе графических процессоров с модификацией, включая специфические алгоритмы распараллеливания, классических методов решения задач математической физики. Потенциальные заказчики находятся в процессе освоения и развития суперЭВМ на базе графических процессоров, а вариант FPGA, как специализированный для решения этих задач, по нашим сведениям, вообще не применяется.

Несмотря на это, социальная значимость этих задач (аэро-, гидро-, термо-, газодинамика) во всем мире чрезвычайно высока.

В части уравнений математической физики основу составляют сложные формализуемые задачи, а часть неформализуемых невелика.

### 4. Big data.

Задача обработки больших массивов данных появилась в последние годы. За рубежом является достаточно социально значимой, в России по объективным причинам менее значима. В литературе практически отсутствует математическая постановка задачи и тем более классификация подзадач на формализуемые и неформализуемые. Поэтому при общем, зачастую эмоциональном, стремлении и желании применять для данной задачи суперЭВМ, для супернейрокомпьютеров место пока не определено.

## 5. Нейроуправление плазмой.

Объективная необходимость перехода в этой важной задаче в нейросетевой логический базис определяется несколькими сотнями зарубежных научных работ. Готовность российских заказчиков к подобному переходу практически нулевая, несмотря на высокую социальную значимость этой задачи за рубежом и излагаемую директивно в России. При этом при переходе на нейросетевой логический базис процессов идентификации плазмы как сложного нелинейного объекта и управления плазмой, задачи являются существенно неформализуемыми. При этом необходимо отметить, что тематика нейроуправления находит применение и для управления другими важными объектами (самолеты, вертолеты, космические корабли и др.)

## 6. Генетика и протеомика.

Создание за последние годы высокопроизводительных систем анализа генома и протеома сделала задачу обработки геномной и протеомной информации задачей big data. За рубежом относительная доля нейросетевых алгоритмов для обработки геномной и протеомной информации в последние годы резко увеличилась.

## 7. Биометрические системы.

Имеет место достаточно активная деятельность по применению нейросетевых технологий в биометрических системах.

#### 8. Модели мозга.

Несмотря на то, что нейрофизиология на протяжении последних более 50 лет мало или вернее ничего не дала развитию сверхвысокопроизводительной вычислительной техники, в частности, нейрокомпьютеров, развитие этой техники является необходимым условием создания эффективных моделей мозга и его разделов, в частности:

- мозжечка;

- гиппокампа;

- базальных ганглиев;

- спинного мозга;

- гипоталамуса;

- генератора дыхательного ритма;

- функционального модуля коры головного мозга;

- системы регуляции внутренних органов;

- системы обоняния и вкуса;

- системы моделирования метаболизма.

Модели разделов мозга должны строиться как нейросетевые вследствие сложности аппроксимируемого объекта. Возможна и необходима реализация этих моделей на GPU и в редких случаях FPGA.

Социальная значимость этих работ за рубежом подтверждается десятками проектов за последние 5-6 лет, в том числе таких как Human Brain и Brain Initiative. Будущие супернейрокомпьютеры с применением мемристоров будут основным средством создания моделей разделов мозга с промежуточной реализацией на FPGA и GPU.

#### 11. Заключение.

Всю историю развития вычислительной техники сопровождают работы по эмуляции алгоритмов искусственного интеллекта, принятия решений и нейронных сетей.

Российские работы по эмуляции нейронных сетей на каждом этапе развития вычислительной техники были связаны с использованием максимально производительных образцов:

- 60-е годы прошлого столетия аналоговые реализации;

- 70-80 годы прошлого столетия программные цифровые реализации;

- 90-е годы прошлого столетия транспьютерные системы, цифровые, аналого-цифровые и аналоговые нейрочипы, ПЛИС;

- 2000-е годы различные нейрочипы, графические процессоры;

- в настоящее время различные нейрочипы, мемристорные системы.

Идеология построения нейрокомпьютеров менялась слабо, менялись и развивались технологии реализации.

Научно-технический задел по созданию отечественных супернейрокомпьютеров экзафлопной производительности с применением мемристоров представлен следующими разделами:

- Теория нейронных сетей, как методика синтеза структур из нейронов различного вида, алгоритмов адаптации весовых коэффициентов в этих структурах в процессе решения различных задач;

- Нейроматематика, как раздел вычислительной математики, связанный с решением в нейросетевом логическом базисе различных сложных формализуемых и неформализуемых задач;

- Нейроуправление, как раздел теории управления, связанный с применением нейрокомпьютеров в качестве систем идентификации сложных динамических систем и нейрокомпьютеров для управления;

- Нейрокомпьютеры и нейрочипы.

Российский опыт работ в области нейросетевых технологий и их применения обобщен в монографии [34]. В данной работе описаны следующие российские научные труды, вышедшие между 1982 и 2010 годами:

- 1. Монографии;

- 2. Кандидатские и докторские диссертации;

- 3. Научно-технические отчеты.

Именно поэтому, когда сейчас говорят: «мемристоры – будущее искусственного мозга», то это вызывает серьезные сомнения и, иногда, улыбку.

На самом деле, мемристоры — это очередной этап эволюционного, гармоничного развития вычислительной техники, в котором за несколько предыдущих десятилетий проведена фундаментальная подготовка к построению высокопроизводительных вычислительных систем, реализующих следующие принципы:

- 1. Переход от классической фон-Неймановской архитектуры к распределенной;

- 2. Возврат в части реализации алгоритмов решения задач к аналоговой обработке с целью увеличения быстродействия при контролируемой точности;

- 3. Переход от представления сигналов в виде уровней токов и напряжений к представлению сигналов в виде частоты последовательности узких импульсов;

- 4. Переход к архитектурам, в которых функции памяти и обработки хотя бы частично совмещены в отличие от классических ЭВМ с полностью распределенными функциями памяти и обработки;

- 5. Переход к нейроматематике нейросетевым алгоритмам решения задач;

- 6. Переход к нейроуправлению нейросетевым алгоритмам и системам управления сложными динамическими объектами;

Модель мозга и его разделов – задачи искусственного интеллекта – важные, но вторичные задачи вычислительной техники, в том числе и для мемристорных систем. Мемристорная система – это просто более эффективный эмулятор нейронных сетей по сравнению в предыдущими типами суперЭВМ. На рис. 32 показано развитие базовых вычислительных платформ для реализации эффективных программных и программно-аппаратных эмуляторов нейронных сетей.

Рис. 32. Создание наиболее эффективных программно-аппаратных эмуляторов нейронных сетей – главная задача нейросетевых технологий.

Несмотря на то, что вычислительная техника за весь большой период существования и развития всегда использовалась для реализации мыслительных функций, только в период 2007-2009 гг. и далее появились работы, в которых показано, что даже самые современные суперЭВМ типа Blue Gene, K-Fujitsu и др. еще крайне недостаточны по производительности для моделирования разделов мозга в реальном времени. Эти исследования показывают, как далека современная (и думаем, что даже перспективная на ближайшее время) технология от технологии реализации аналогов реального живого мозга, и как далеки мы от настоящего, глубокого понимания принципов работы живого мозга, которые мы сможем использовать при построении искусственных систем.

С этой точки зрения, мемристоры – это не шаг к модели мозга, а небольшой шаг в развитии высокопроизводительной вычислительной техники, который позволит создать более эффективные эмуляторы нейронных сетей и более быстро и качественно решать инженерные задачи следовательно:

- Мемристоры эволюционное развитие микроэлектроники в сторону нанотехнологий;

- Нейрокомпьютеры с применением мемристоров эволюционное развитие высокопроизводительной техники.

Вследствие этого некорректно использовать в работах по применению мемристоров в нейрокомпьютерах: "Brains are made of Memristors", "to act more like Brains", "Biologically inspired Electronic", "Brain models" и подобные.

Мемристорные системы имеют такое же далекое отношение к моделям мозга, как нейрокомпьютеры 60-х гг. прошлого века, IBM Computer 70-х и т.д.

На рис. 33 условно представлено мнение автора о взаимоотношении разработок сверхвысокой высокопроизводительной техники, в том числе и супернейрокомпьютеров, и нейрофизиологии. Исходя из данной схемы эти два направления соединяют четыре проблемы:

- эмуляция нейронных сетей для решения технических задач;

- интерфейс «мозг компьютер»;

- нейроимплантанты;

- искуственный мозг.

В части эмуляции нейронных сетей для решения технических задач с нашей точки зрения роль нейрофизиологии для развития вычислительных систем практически нулевая. Высокопроизводительные вычислительные системы используются в нейрофизиологии для эмуляции больших нейросетевых образований. В настоящее время эта процедура, реализуемая на ЭВМ IBM Blue Gene и Fujitsu K, показывает, что возможности современных суперЭВМ для моделирования разделов мозга крайне незначительны.

В части интерфейса «мозг – компьютер» нейрофизиология может оказать значительную помощь вычислительной техники в части новых методов управления вычислительными системами.

В части нейроимплантантов вычислительные системы являются основой их технической реализации.

Проблема «Искусственный мозг» является в настоящее время с нашей точки зрения, чисто искусственной, т.к. технологии реализации вычислительных систем резко отличаются от технологий реализации живого мозга и переносимость результатов с одного на другое является чисто условной.

Необходимо отметить основные перспективные направления работ по созданию нейрокомпьютеров с применением мемристоров с ориентацией на большие нейронные сети:

- \* Выбор технологии с точки зрения обеспечения максимальной производительности

- \* Разработка вариантов архитектуры и схемотехники СБИС-нейрочипов с применением мемристоров

- \* Разработка вариантов архитектуры и схемотехники нейроплат, нейроблоков и нейростоек нейрокомпьютеров с применением мемристоров

- \* Разработка алгоритмов адаптации нейронных сетей, адекватных архитектурам с применением мемристоров и с учетом моделей мемристоров;

- \* Разработка нейросетевых алгоритмов решения задач, адекватных архитектурам с применением мемристоров

- \* Разработка алгоритмов распараллеливания нейросетевых структур, адекватных архитектурам с применением мемристоров

- \* Разработка методики оценки производительности, адекватной архитектуре с применением мемристоров.

Оценить необходимость и важность очередного шага в развитии сверхвысокопроизводительной вычислительной техники может её пользователь, но при следующем необходимом условии: пользователь должен освоить в достаточной степени последний шаг и понять его ограничения по критерию отношения производительности к

стоимости (или габаритам). Поэтому бесполезно предлагать оценить важность мемристорных вычислительных систем пользователям, которые недостаточно полно освоили для решения своих задач суперЭВМ на базе графических процессоров.

# Литература

- 1. Бёрд Киви К точке критического перехода. 3D-News (Daily Digital Digest). 29.05.2013 г.

- 2. *Amber McKenzie and oth* Toward Exascale Computing through Neuromorphic Approaches Sandia Report, Sand 2010 6312. September 2010.

- 3. *Галушкин А.И*. Стратегия развития современных супернейрокомпьютеров на пути к экзафлопным вычислениям. Приложение к журналу «Информационные технологии» № 3, 2012 г.

- 4. *Галушкин А.И*. Многослойные системы распознавания образов. Из-во МИЭМ, монография, М. 1970.

- 5. *Галушкин А.И.* Синтез многослойных систем распознавания образов. Из-во "Энергия", М. 1974.

- 6. *Галушкин А.И.* Теория нейронных сетей. Книга 1 серии «Нейрокомпьютеры и их применение» Из-во «Радиотехника», М. 2000 г.

- 7. *Галушкин А.И., Цыпкин Я.3*. Нейронные сети: история развития теории. Книга 5 серии «Нейрокомпьютеры и их применение» Из-во «Радиотехника», М. 2001 г.

- 8. *Галушкин А.И.* Теория нейронных сетей. Издательство университета Синьхуа г. Пекин (на китайском языке) 2003 г.

- 9. Galushkin A.I.. Neural Network Theory. «Springer» 2007 Γ.

- 10.  $\Gamma$ алушкин A.И. Нейронные сети: основы теории. Из-во «Горячая линия Телеком», М. 2010 г.

- 11. Нейроматематика. Книга 6 серии «Нейрокомпьютеры и их применение» Изво «Радиотехника», М. 2002 г.

- 12.  $\Gamma$ алушкин A.И. Нейроматематика (проблемы развития). «Нейрокомпьютер» №1, 2003 г.

- 13. *Галушкин А.И*. Методика решения задач в нейросетевом логическом базисе. Приложение к журналу «Информационные технологии» №6, 2006 г.

- 14. *Терехов В.А. и др.* Нейросетевые системы управления. Книга 8 серии «Нейрокомпьютеры и их применение» Из-во «Радиотехника», М. 2004 г.

- 15. *Галушкин А.И*. Основы нейроуправления. Приложение к журналу «Информационные технологии» № 10, 2002 г.

- 16. Аналоговые запоминающие и адаптивные элементы (под ред. Б.С. Сотскова). Из-во "Энергия", М. 1973 г.

- 17. *Трейер В.В., Елизаров А.Б.* Электрохимические интегрирующие и аналоговые запоминающие элементы. Из-во "Энергия", М. 1973 г.

- 18. *Галушкин А.И.* Нейрокомпьютеры. Книга 1 серии «Нейрокомпьютеры и их применение» Из-во «Радиотехника», М. 2000 г.

- 19. Нейрокомпьютеры: от программной к аппаратной реализации. Из-во «Горячая линия Телеком», М. 2006 г.

- 20. S. Shin, K. Kim and S.M. Kang Memristors and Their Applications for Nanocomputing. IEEE Trans. on Nanotechnology, Mar. 2011io

- 21. *Harika Manem, Jeyavijayan Rajendran, Garrett S. Rose* Stochastic Gradient Descent Inspired Training Technique for a CMOS/Nano Memristive Trainable Threshold Gate Array. IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS–I: REGULAR PAPERS, VOL. 59, NO. 5, MAY 2012.

- 22. ADHIKARI et al. Memristor Bridge Synapse-Based Neural Network and Its Learning. IEEE TRANSACTIONS ON NEURAL NETWORKS AND LEARNING SYSTEMS, VOL 23, NO 9 SEPTEMBER 2012.

- 23. Maheshwar Pd. Sah, Changju Yang, Hyongsuk Kim and Leon O Chua Meristor Circuit for Artificial Synaptic Weighting of Pulse Inputs. Circuits and Systems (ISCAS), 2012 IEEE International Symposium.

- 24. *Maheshwar Pd. Sah, Changju Yang, Ram Kaji Budhathoki and Hyongsuk Kim* Features of memristor emulator-based artificial neural synapses. Circuits and Systems (ISCAS), 2012 IEEE International Symposium.

- 25. *Young-Su Kim, Kyeong-Sik Min* Synaptic weighting circuits for Cellular Neural Networks. Cellular Nanoscale Networks and Their Applications (CNNA), 2012 13th International Workshop.

- 26. Thomas John Walls, Konstantin K. Likharev Self-Organization in Autonomous, Recurrent, Firing-Rate CrossNets With Quasi-Hebbian Plasticity. IEEE Transactions on Neural Networks and Learning Systems, Vol. 25, №4, APRIL 2014.

- 27. *Hebb D.O.* The organization of Behavior: A Neuropsyhological Theory. New York: Wiley, June 1949.

- 28. Gorchetchnikov A., Versace M., Ames H., Chandler B., Leveille J., Livitz G., Mingolla E., Snider G., Amerson R., Carter D., Abdalla H., Qureshi M.S. Review and unification of learning framework in Cog Ex Machina platform for memristive neuromorphic hardware. Proceedings of International Joint Conference on Neural Networks, San Jose, California, USA, July 31 August 5, 2011.

- 29. *Jae-sun Seo et al.* A 45nm CMOS neuromorphic chip with a scalable architecture for learning in networks of spiking neurons. Custom Integrated Circuits Conference (CICC), 2011 IEEE

- 30. Serrano-Gotarredona T., Prodromakis T., Linares-Barranco B. A Proposal for Hybrid Memristor-CMOS Spiking Neuromorphic Learning Systems. IEEE Circuits and Systems Magazine, (Volume:13, Issue: 2)

- 31. *Yongtae Kim, Yong Zhang, Peng Li* A digital neuromorphic VLSI architecture with memristor crossbar synaptic array for machine learning. IEEE International SOC Conference (SOCC), 2012.

- 32. Azghadi M.R., Moradi S., Indiveri G. Programmable neuromorphic circuits for spike-based neural dynamics. IEEE 11th International New Circuits and Systems Conference (NEWCAS), 2013.

- 33. *Kaneko Y., Nishitani Yu., Ueda M., Tsujimura A.* Neural network based on a three-terminal ferroelectric memristor to enable on-chip pattern recognition. 2013 Symposium VLSI Technology (VLSIT).

- 34.  $\Gamma$ алушкин А.И., Симоров С.Н. Нейросетевые технологии в России (1982-2010 г.). Из-во «Горячая линия Телеком», М. 2011 г.

- 35. Применение искусственных нейронных сетей и системы остаточных классов в криптографии М. Физматлит. 2012 (колл. авторов)

#### References

- 1. Bjord Kivi K tochke kriticheskogo perehoda. 3D-News (Daily Digital Digest). 29.05.2013 g.

- 2. Amber McKenzie and oth Toward Exascale Computing through Neuromorphic Approaches Sandia Report, Sand 2010 6312. September 2010.

- 3. Galushkin A.I. Strategija razvitija sovremennyh supernejrokomp'juterov na puti k jekzaflopnym vychislenijam. Prilozhenie k zhurnalu «Informacionnye tehnologii» № 3, 2012 g.

- 4. Galushkin A.I. Mnogoslojnye sistemy raspoznavanija obrazov. Iz-vo MIJeM, monografija, M. 1970.

- 5. Galushkin A.I. Sintez mnogoslojnyh sistem raspoznavanija obrazov. Iz-vo "Jenergija", M. 1974.

- 6. Galushkin A.I. Teorija nejronnyh setej. Kniga 1 serii «Nejrokomp'jutery i ih primenenie» Iz-vo «Radiotehnika», M. 2000 g.

- 7. Galushkin A.I., Cypkin Ja.3. Nejronnye seti: istorija razvitija teorii. Kniga 5 serii «Nejrokomp'jutery i ih primenenie» Iz-vo «Radiotehnika», M. 2001 g.

- 8. Galushkin A.I. Teorija nejronnyh setej. Izdatel'stvo universiteta Sin'hua g. Pekin (na kitajskom jazyke) 2003 g.

- 9. Galushkin A.I.. Neural Network Theory. «Springer» 2007 g.

- 10. Galushkin A.I. Nejronnye seti: osnovy teorii. Iz-vo «Gorjachaja linija Telekom», M. 2010 g.

- 11. Nejromatematika. Kniga 6 serii «Nejrokomp'jutery i ih primenenie» Iz-vo «Radiotehnika», M. 2002 g.

- 12. Galushkin A.I. Nejromatematika (problemy razvitija). «Nejrokomp'juter» №1, 2003 g.

- 13. Galushkin A.I. Metodika reshenija zadach v nejrosetevom logicheskom bazise. Prilozhenie k zhurnalu «Informacionnye tehnologii» №6, 2006 g.

- 14. Terehov V.A. i dr. Nejrosetevye sistemy upravlenija. Kniga 8 serii «Nejrokomp'jutery i ih primenenie» Iz-vo «Radiotehnika», M. 2004 g.

- 15. Galushkin A.I. Osnovy nejroupravlenija. Prilozhenie k zhurnalu «Informacionnye tehnologii» № 10, 2002 g.

- 16. Analogovye zapominajushhie i adaptivnye jelementy (pod red. B.S. Sotskova). Izvo "Jenergija", M. 1973 g.

- 17. Trejer V.V., Elizarov A.B. Jelektrohimicheskie integrirujushhie i analogovye zapominajushhie jelementy. Iz-vo "Jenergija", M. 1973 g.

- 18. Galushkin A.I. Nejrokomp'jutery. Kniga 1 serii «Nejrokomp'jutery i ih primenenie» Iz-vo «Radiotehnika», M. 2000 g.

- 19. Nejrokomp'jutery: ot programmnoj k apparatnoj realizacii. Iz-vo «Gorjachaja linija Telekom», M. 2006 g.

- 20. S. Shin, K. Kim and S.M. Kang Memristors and Their Applications for Nanocomputing. IEEE Trans. on Nanotechnology, Mar. 2011ju

- 21. Harika Manem, Jeyavijayan Rajendran, Garrett S. Rose Stochastic Gradient Descent Inspired Training Technique for a CMOS/Nano Memristive Trainable Threshold Gate Array. IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS–I: REGULAR PAPERS, VOL. 59, NO. 5, MAY 2012.

- 22. ADHIKARI et al. Memristor Bridge Synapse-Based Neural Network and Its Learning. IEEE TRANSACTIONS ON NEURAL NETWORKS AND LEARNING SYSTEMS, VOL 23, NO 9 SEPTEMBER 2012.

- 23. Maheshwar Pd. Sah, Changju Yang, Hyongsuk Kim and Leon O Chua Meristor Circuit for Artificial Synaptic Weighting of Pulse Inputs. Circuits and Systems (ISCAS), 2012 IEEE International Symposium.

- 24. Maheshwar Pd. Sah, Changju Yang, Ram Kaji Budhathoki and Hyongsuk Kim Features of memristor emulator-based artificial neural synapses. Circuits and Systems (ISCAS), 2012 IEEE International Symposium.

- 25. Young-Su Kim, Kyeong-Sik Min Synaptic weighting circuits for Cellular Neural Networks. Cellular Nanoscale Networks and Their Applications (CNNA), 2012 13th International Workshop.

- 26. Thomas John Walls, Konstantin K. Likharev Self-Organization in Autonomous, Recurrent, Firing-Rate CrossNets With Quasi-Hebbian Plasticity. IEEE Transactions on Neural Networks and Learning Systems, Vol. 25, №4, APRIL 2014.

- 27. Hebb D.O. The organization of Behavior: A Neuropsyhological Theory. New York: Wiley, June 1949.

- 28. Gorchetchnikov A., Versace M., Ames H., Chandler B., Leveille J., Livitz G., Mingolla E., Snider G., Amerson R., Carter D., Abdalla H., Qureshi M.S. Review and unification of learning framework in Cog Ex Machina platform for memristive neuromorphic hardware. Proceedings of International Joint Conference on Neural Networks, San Jose, California, USA, July 31 August 5, 2011.

- 29. Jae-sun Seo et al. A 45nm CMOS neuromorphic chip with a scalable architecture for learning in networks of spiking neurons. Custom Integrated Circuits Conference (CICC), 2011 IEEE

- 30. Serrano-Gotarredona T., Prodromakis T., Linares-Barranco B. A Proposal for Hybrid Memristor-CMOS Spiking Neuromorphic Learning Systems. IEEE Circuits and Systems Magazine, (Volume:13, Issue: 2)

- 31. Yongtae Kim, Yong Zhang, Peng Li A digital neuromorphic VLSI architecture with memristor crossbar synaptic array for machine learning. IEEE International SOC Conference (SOCC), 2012.

- 32. Azghadi M.R., Moradi S., Indiveri G. Programmable neuromorphic circuits for spike-based neural dynamics. IEEE 11th International New Circuits and Systems Conference (NEWCAS), 2013.

- 33. Kaneko Y., Nishitani Yu., Ueda M., Tsujimura A. Neural network based on a three-terminal ferroelectric memristor to enable on-chip pattern recognition. 2013 Symposium VLSI Technology (VLSIT).

- 34. Galushkin A.I., Simorov S.N. Nejrosetevye tehnologii v Rossii (1982-2010 g.). Iz-vo «Gorjachaja linija Telekom», M. 2011 g.

- 35. Primenenie iskusstvennyh nejronnyh setej i sistemy ostatochnyh klassov v kriptografii M. Fizmatlit. 2012 (koll. avtorov)